# **TYPICAL QUESTIONS & ANSWERS**

## PART – I

## **OBJECTIVE TYPE QUESTIONS**

## Each Question carries 2 marks.

#### Choose the correct or best alternative in the following:

Q.1 If the crystal oscillator is operating at 15 MHz, the PCLK output of 8284 is

(A) 2.5 MHz.

(B) 5 MHz.

(C) 7.5 MHz.

(D) 10 MHz.

Ans: (A)

**Q.2** In which T-state does the CPU sends the address to memory or I/O and the ALE signal for demultiplexing

| (A) T1.          | <b>(B)</b> T2. |

|------------------|----------------|

| ( <b>C</b> ) T3. | <b>(D)</b> T4. |

**Ans**, During the first clocking period in a bus cycle, which is called T1, the address of the memory or I/O location is sent out and the control signals ALE, DT/R' and IO/M' are also output. Hence answer is (A).

**Q.3** If a  $1M \times 1$  DRAM requires 4 ms for a refresh and has 256 rows to be refreshed, no more than \_\_\_\_\_\_ of time must pass before another row is refreshed.

| ( <b>A</b> ) 64 ms.  | <b>(B)</b> 4 ns.      |

|----------------------|-----------------------|

| ( <b>C</b> ) 0.5 ns. | <b>(D)</b> 15.625 μs. |

**Ans** Answer is (B)

Q.4 In a DMA write operation the data is transferred

(A) from I/O to memory.

(B) from memory to I/O.

(C) from memory to memory.

(D) from I/O to I/O.

**Ans** A DMA writes operation transfers data from an I/O device to memory. Hence answer is (A).

Q.5 Which type of JMP instruction assembles if the distance is 0020 h bytes

(A) near.

(B) far.

(C) short.

(D) none of the above.

Ans The three byte near jump allows a branch or jump within  $\pm$  32K bytes. Hence answer is (A).

- **Q.6** A certain SRAM has  $\overline{CS} = 0$ ,  $\overline{WE} = 0$  and  $\overline{OE} = 1$ . In which of the following modes this SRAM is operating

- (A) Read (B) Write

(C) Stand by

**(D)** None of the above

**Ans** For CS'=WE'=0, write operation. Hence answer is (B).

- **Q.7** Which of the following is true with respect to EEPROM?

- (A) contents can be erased byte wise only.

- (B) contents of full memory can be erased together.

- (C) contents can be erased using ultra violet rays

- (D) contents can not be erased

**Ans** Answer is (C).

- **Q.8** Pseudo instructions are basically

- (A) false instructions.

- (B) instructions that are ignored by the microprocessor.

- (C) assembler directives.

- (D) instructions that are treated like comments.

Ans Pseudo-instructions are commands to the assembler. All pseudo-operations start with a period. Pseudo-instructions are composed of a pseudo-operation which may be followed by one or more expressions. Hence answer is (C).

Q.9 Number of the times the instruction sequence below will loop before coming out of loop is

| MOV AL, 00h     |                |

|-----------------|----------------|

| A1: INC AL      |                |

| JNZ A1          |                |

| ( <b>A</b> ) 00 | <b>(B)</b> 01  |

| (C) 255         | <b>(D)</b> 256 |

**Ans** Answer is (D)

Q.10 What will be the contents of register AL after the following has been executed MOV BL, 8C MOV AL, 7E ADD AL, BL (A) 0A and carry flag is set (B) 0A and carry flag is reset

(**D**) 6A and carry flag is reset

Ans, Result is 1,0A. Hence answer is (A).

(C) 6A and carry flag is set

- Direction flag is used with Q.11

- (A) String instructions.

- **(B)** Stack instructions.

- (C) Arithmetic instructions. **(D)** Branch instructions.

**Ans** The direction flag is used only with the string instructions. Hence answer is (A).

- Q.12 Ready pin of a microprocessor is used

- (A) to indicate that the microprocessor is ready to receive inputs.

- (B) to indicate that the microprocessor is ready to receive outputs.

- (C) to introduce wait states.

AC23

(D) to provide direct memory access.

**Ans** This input is controlled to insert wait states into the timing of the microprocessor. Hence answer is (C).

## Q.13 These are two ways in which a microprocessor can come out of Halt state.

- (A) When hold line is a logical 1.

- (B) When interrupt occurs and the interrupt system has been enabled.

- (C) When both (A) and (B) are true.

- (D) When either (A) or (B) are true.

**Ans** Answer is (A)

- **Q.14** In the instruction FADD, F stands for

- (A) Far.(B) Floppy.(C) Floating.(D) File.

Ans Adds two floating point numbers. Hence answer is (C).

Q.15 SD RAM refers to

| (A)          | Synchronous DRAM | (B) Static DRAM          |

|--------------|------------------|--------------------------|

| ( <b>C</b> ) | Semi DRAM        | ( <b>D</b> ) Second DRAM |

Ans, Answer is (A)

Q.16 In case of DVD, the speed is referred in terms of n X (for example 32 X). Here, X refers to

(A) 150 KB/s

(B) 300 KB/s

| (A)        | 150 KB/s  | <b>(B)</b> 300 KB/s |

|------------|-----------|---------------------|

| <b>(C)</b> | 1.38 MB/s | <b>(D)</b> 2.4 MB/s |

Ans Answer is (C).

- Q.17 Itanium processor of Intel is a

- (A) 32 bit microprocessor.

- (C) 128 bit microprocessor.

**(B)** 64 bit microprocessor.

**(D)** 256 bit microprocessor.

Ans The Itanium is a 64-bit architecture microprocessor. Hence answer is (B).

Q.18 LOCK prefix is used most often

(A) during normal execution.

(C) during interrupt servicing.

(B) during DMA accesses

(D) during memory accesses.

**Ans** LOCK is a prefix which is used to make an instruction of 8086 non-interruptable.

Hence answer is (C).

- Q.19 The Pentium microprocessor has \_\_\_\_\_execution units. (A) 1 (B) 2

- (C) 3 (D) 4

**Ans** The Pentium microprocessor is organized with three execution units. One executes floating-point instructions, and the other two (U-pipe and V-pipe) execute

integer instructions. Hence answer is (C).

**Q.20** EPROM is generally erased by using

| (A) Ultraviolet rays      |  |

|---------------------------|--|

| (C) 12 V electrical pulse |  |

(B) infrared rays(D) 24 V electrical pulse

**Ans** The EPROM is erasable if exposed to high-intensity ultraviolet light for about 20 minutes or less. Hence answer is (A)

- Q.21 Signal voltage ranges for a logic high and for a logic low in RS-232C standard are

- (A) Low = 0 volt to 1.8 volt, high = 2.0 volt to 5 volt

- (B) Low =-15 volt to -3 vol, high = +3 volt to +15 volt

- (D) Low = +3 volt to +15 volt, high = -3 volt to -15 volt

- (E) Low = 2 volt to 5.0 volt, high = 0 volt to 1.8 volt

**Ans** Answer is (B)

- Q.22 The PCI bus is the important bus found in all the new Pentium systems because(A) It has plug and play characteristics

- (B) It has ability to function with a 64 bit data bus

- (C) Any Microprocessor can be interfaced to it with PCI controller or bridge

- **(D)** All of the above

Ans, Answer is (D).

- **Q.23** Which of the following statement is true?

- (A) The group of machine cycle is called a state.

- (B) A machine cycle consists of one or more instruction cycle.

- (C) An instruction cycle is made up of machine cycles and a machine cycle is made up of number of states.

- **(D)** None of the above

Ans An instruction cycle consists of several machine cycles. Hence Answer is (B).

- **Q.24** 8251 is a

- (A) UART

- (B) USART

- (C) Programmable Interrupt controller

- (D) Programmable interval timer/counter

Ans The Intel 8251 is a programmable communication interface. It is USART.

Q.25 8088 microprocessor has

| (A) 16 bit data bus        | ( <b>B</b> ) 4 byte pre-fetch queue |

|----------------------------|-------------------------------------|

| (C) 6 byte pre-fetch queue | ( <b>D</b> ) 16 bit address bus     |

**Ans** The 8088 is a 16-bit microprocessor with an 8-bit data bus. The 16-bit address bus. Hence answer is (D).

|                                                                                                                                                                |                                                                                                                                           | Mici opi ocessor Duseu Bystem Des                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|

| Q.26                                                                                                                                                           | By what factor does the 8284A clock frequency?                                                                                            | generator divide the crystal oscillator's output                                               |  |

|                                                                                                                                                                | · ·                                                                                                                                       |                                                                                                |  |

|                                                                                                                                                                | (A) One                                                                                                                                   | ( <b>B</b> ) Two                                                                               |  |

|                                                                                                                                                                | (C) Three                                                                                                                                 | ( <b>D</b> ) Four                                                                              |  |

|                                                                                                                                                                | <b>Ans</b> When F/C' is at logic 0; The os by-3 counter. Hence answer is (c).                                                             | cillator output is steered through to the divide-                                              |  |

| Q.27                                                                                                                                                           | The memory data bus width in Pentiu                                                                                                       | m is                                                                                           |  |

|                                                                                                                                                                | ( <b>A</b> ) 16 bit                                                                                                                       | <b>(B)</b> 32 bit                                                                              |  |

|                                                                                                                                                                | ( <b>C</b> ) 64 bit                                                                                                                       | ( <b>D</b> ) None of these                                                                     |  |

|                                                                                                                                                                | Ans The Data bus width is 64 bits. He                                                                                                     | ence answer is (C).                                                                            |  |

| Q.28                                                                                                                                                           | When the 82C55 is reset, its I/O ports                                                                                                    | are all initializes as                                                                         |  |

| <b>X</b> 0                                                                                                                                                     | (A) output port using mode 0                                                                                                              |                                                                                                |  |

|                                                                                                                                                                | (C) output port using mode 1                                                                                                              |                                                                                                |  |

|                                                                                                                                                                |                                                                                                                                           |                                                                                                |  |

|                                                                                                                                                                | Ans A RESET input to the 82C55 ca<br>using mode 0 operations. Hence answ                                                                  | uses all ports to be set up as simple input ports yer is (D).                                  |  |

| Q.29                                                                                                                                                           | Which microprocessor pins are used                                                                                                        | to request and acknowledge a DMA transfer?                                                     |  |

| -                                                                                                                                                              | (A) reset and ready                                                                                                                       | $(\hat{\mathbf{B}})$ ready and wait                                                            |  |

|                                                                                                                                                                | (C) HOLD and HLDA                                                                                                                         | ( <b>D</b> ) None o these                                                                      |  |

|                                                                                                                                                                |                                                                                                                                           | is used request a DMA action and the HLDA<br>s the DMA action. Hence answer is (C).            |  |

| <ul><li>Q.30 Which of the following statement is false?</li><li>(A) RTOS performs tasks in predictable amount of time</li><li>(B) Windows 98 is RTOS</li></ul> |                                                                                                                                           |                                                                                                |  |

|                                                                                                                                                                | (C) Interrupts are used to develop                                                                                                        | RTOS                                                                                           |  |

|                                                                                                                                                                | ( <b>D</b> ) Kernel is the one of component of any OS                                                                                     |                                                                                                |  |

|                                                                                                                                                                | <b>Ans</b> Operating systems, like Windows, defer many tasks and do not guarantee the execution in predictable time. Hence answer is (B). |                                                                                                |  |

| Q.31                                                                                                                                                           | The VESA local bus operates at                                                                                                            |                                                                                                |  |

| L.                                                                                                                                                             | (A) 8 MHz                                                                                                                                 | ( <b>B</b> ) 33 MHz                                                                            |  |

|                                                                                                                                                                | (C) 16 MHz                                                                                                                                | (D) None of these                                                                              |  |

|                                                                                                                                                                | Ans The VESA local bus operates at 33 MHz. Hence answer is (B).                                                                           |                                                                                                |  |

| Q.32                                                                                                                                                           | The first modern computer was ca                                                                                                          | lled                                                                                           |  |

| <b>X</b> -0-                                                                                                                                                   | (A) FLOW-MATIC                                                                                                                            | (B) UNIVAC-I                                                                                   |  |

|                                                                                                                                                                | (C) ENIAC                                                                                                                                 | (D) INTEL                                                                                      |  |

|                                                                                                                                                                |                                                                                                                                           | , ,                                                                                            |  |

|                                                                                                                                                                |                                                                                                                                           | ntegrator And Computer) was the first general-<br>Turing-complete, digital computer capable of |  |

5

being reprogrammed to solve a full range of computing problems. ENIAC was

designed to calculate artillery firing tables for the U.S. Army's Ballistic Research Laboratory. Hence answer is (c).

#### 0.33 Software command CLEAR MASK REGISTER in DMA

- (A) Disables all channels.

- (B) Enables all channels.

(C) None.

(**D**) Clears first/last flip-flop within 8237.

Ans Enables all four DMA channels. Hence answer is (B).

**Q.34** The first task of DOS operating system after loading into the memory is to use the file called

| (A) HIMEM.SYS    | ( <b>B</b> ) CONFIG.SYS |

|------------------|-------------------------|

| (C) AUTOEXEC.BAT | (D) SYSTEM.INI          |

Ans, The first task of the DOS operating system, after loading into memory, is to use a file called the CONFIG.SYS file. This file specifies various drivers that load into the memory, setting up or configuring the machine for operation under DOS.

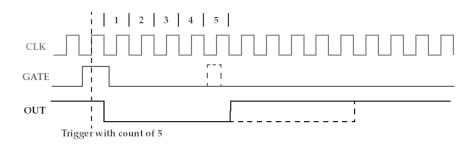

**Q.35** If the programmable counter timer 8254 is set in mode 1 and is to be used to count six events, the output will remain at logic 0 for \_\_\_\_\_ number of counts (A) 5 **(B)** 6 **(C)** 0 **(D)** All of the above

Ans. OUT continues for the total length of the count. Hence answer is (B).

Q.36 The flash memory is programmed in the system by 12 V programming pulse.

> (A) TRUE (B) FALSE

**Ans** The flash memory device requires a 12V programming voltage to erase and write new data. Hence answer is (A).

**Q.37** A plug and play (PnP) interface is one that contains a memory that holds configuration information of the system. (A) TRUE (B) FALSE

**Ans** Answer is (A)

Q.38 The accelerated graphics port (AGP) allows virtually any microprocessor to be interfaced with PCI bus via the use of bridge interface. (A) TRUE (B) FALSE

Ans, this port probably will never be used for any devices other than the video card. Hence answer is (B).

**Q.39** A Bus cycle is equal to how many clocking periods

| (A) Two  | (B) Three |

|----------|-----------|

| (C) Four | (D) Six   |

Ans Typically, the bus-cycle of the 8086 and 8088 processors consist of four clock cycles or pulses. Thus, duration of a bus-cycle is = '4\*T'. Hence Answer is (C).

Q.40 The time required to refresh a typical DRAM is

| (A) $2 - 4$ us | (B) 2 – 4 ns |

|----------------|--------------|

| (C) 2 – 4 ms   | (D) 2 – 4 ps |

Ans The capacitor Cs discharges through the internal resistance of the NMOS transistor T1. Typically Cs = 0.2 pF and the internal resistance Rin =  $10^{10}$  ohms, so: Cs x Rin =  $0.2 \times 10^{-12} \times 10^{10} \times 10^{3}$  ms = 2 ms So the typical refresh time interval is 2 ms. Hence Answer is (C).

Q.41 The no. of address lines required to address a memory of size 32 K is

| (A) 15 lines | (B) 16 lines |

|--------------|--------------|

| (C) 18 lines | (D) 14 lines |

**Ans**  $32K = 32 \times 1024$  bits =  $2^5 \times 2^{10} = 2^{15}$  Hence answer is (A).

Q.42 The no. of wait states required to interface 8279 to 8086 with 8MHz clock are

| (A) Two | (B) Three |

|---------|-----------|

| (C) One | (D) None  |

**Ans** Two wait states used so that device can function with an 8 MHz. Hence answers is (A).

Q.43 NMI input is

| (A) Edge sensitive                | (B) Level sensitive                    |

|-----------------------------------|----------------------------------------|

| (C) Both edge and level triggered | (D) edge triggered and level sensitive |

**Ans** Non-maskable interrupt (NMI) is an **edge –triggered** input that requests an interrupt on the positive edge (0 to 1 transition).

| Q.44 | Data rate available for use on USB is           |                                   |

|------|-------------------------------------------------|-----------------------------------|

|      | (A) 12 Mbits per second                         | ( <b>B</b> ) 1.5 Mbits per second |

|      | ( <b>C</b> ) Both ( <b>A</b> ) and ( <b>B</b> ) | ( <b>D</b> ) No restriction       |

**Ans** Data transfer speeds are 12 Mbps for full speed operation and 1.5 Mbps for slow speed operation. Hence answer is (c).

| Q.45 | In 80186, the timer which | connects to the system clock is       |

|------|---------------------------|---------------------------------------|

|      | ( <b>A</b> ) timer 0      | <b>(B)</b> timer 1                    |

|      | ( <b>C</b> ) timer 2      | ( <b>D</b> ) Any one can be connected |

Ans. Timer 2 is internal and clocked by the master clock. Hence answer is (c).

| Q.46 | Conversion of the +1000 decimal | number into signed binary word results |

|------|---------------------------------|----------------------------------------|

|      | (A) 0000 0011 1110 1000         | (B) 1111 1100 0001 1000                |

|      | (C) 1000 0011 1110 1000         | (D) 0111 1100 0001 1000                |

Ans

|      | $1000 /2 =>500 \rightarrow 0$<br>$500/2 =>250 \rightarrow 0$<br>$250/2 =>125 \rightarrow 0$<br>$125/2 =>62 \rightarrow 1$<br>$62/2 =>31 \rightarrow 0$<br>$31/2 =>15 \rightarrow 1$<br>$15/2 =>7 \rightarrow 1$<br>$7/2 =>3 \rightarrow 1$<br>$3/2 =>1 \rightarrow 1$<br>16 bit signed number is 1000<br>Hence Answer is (C). | 0,0011,1110,1000                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Q.47 | What do the symbols [] indicate?<br>(A) Direct addressing<br>(C) Indirect addressing                                                                                                                                                                                                                                          | <ul><li>(B) Register Addressing</li><li>(D) None of the above</li></ul> |

|      | Ans Answer is (C).                                                                                                                                                                                                                                                                                                            |                                                                         |

| Q.48 | SDRAM refers to<br>(A) static DRAM<br>(C) sequential DRAM                                                                                                                                                                                                                                                                     | <ul><li>(B) synchronous DRAM</li><li>(D) semi DRAM</li></ul>            |

|      | Ans, Answer is (B)                                                                                                                                                                                                                                                                                                            |                                                                         |

|      |                                                                                                                                                                                                                                                                                                                               |                                                                         |

Q.49 Which pins are general purpose I/O pins during mode-2 operation of the 82C55? (A) PA0 – PA7 (B) PB0-PB7 (C) PC3-PC7 (D) PC0-PC2

**Ans** In mode 2 Port-A can be programmed to operate as bidirectional port. The mode-2 operation is only for Port-A. Hence Answer is (A)

## PART – II

# **DESCRIPTIVES**

Q.1 Describe the operation performed by the instruction OUT 47 h, AL. (3)

**Ans :** It transfers the content of AL to I/O port 47h. Notice that I/O port number appears as 0047h on the 16 bit address bus and that data from AL appears on the data bus of the microprocessor.

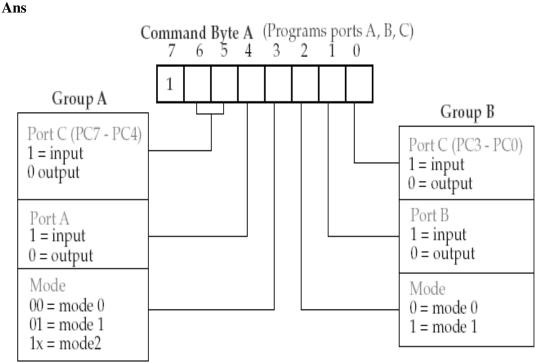

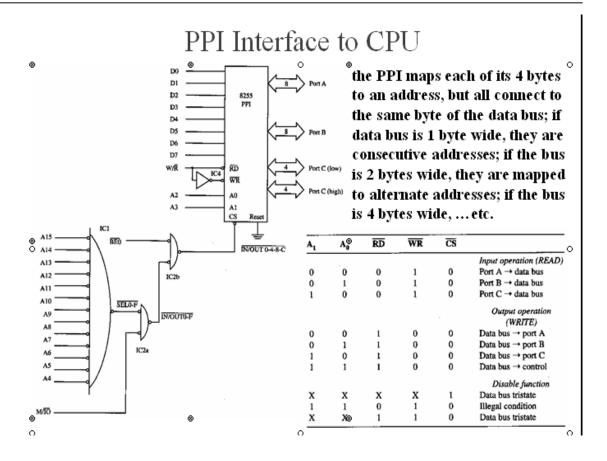

Q.2 How is 8255 (Programmable Peripheral Interface) configured if its control register contains 9B h. (3)

# c

9BH => 1001 1011 => b6b5=00-> Mode0 b4=0-> Port A as input. b3=1-> Port C as input (PC7-PC4) b2=0-> Mode 0 b1=1-> Port B as input b0=1-> Port C as input (PC3-PC0).

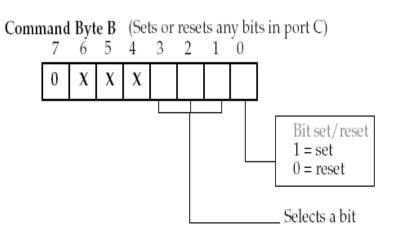

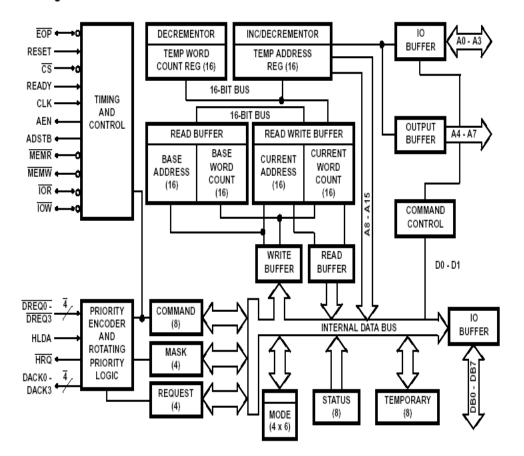

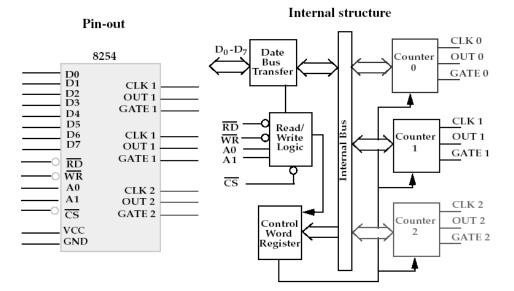

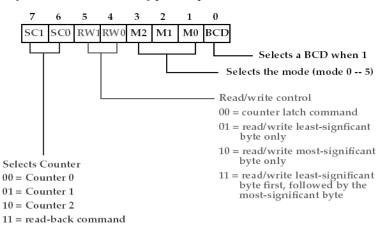

Q.3 Write a control word for counter 1 of 8253 / 8254 that selects the following options: load least significant byte only, mode 5 of operation and binary counting. Then write an instruction sequence that will load the control word into 8253 / 8254 that is located at address 01000 h of memory address space. Assume that 8253 / 8254 is attached to the I/O bus of the CPU and the address inputs A<sub>0</sub> and A<sub>1</sub> are supplied by A<sub>2</sub> and A<sub>3</sub> respectively. (5)

Ans

8253/54 Control Word Format

Based on the above given conditions and assuming counter 0 is used. The control word becomes 0001 1010h.

Identify the port address

- The CS is enabled when A7=1

- The Control Register is selected when A1 and A0 = 1

- Assuming unused address lines A6 to A2 are at logic 0,

Then port address will be as follows

Control Register = 83H Counter 2 = 82HMVI A, B0H OUT 83H MVI A, LOWBYTE OUT 82H **MVI A, HIGHBYTE** OUT 82H LOOP:MVI A.80H OUT 83H **IN 82H** MOV D,A IN 82H ORA D JNZ LOOP RET

Q.4 'Pentium processor has a superscalar architecture'. Explain the meaning of the statement. (4)

## Ans

The Pentium microprocessor is organized with three execution units. One executes floating-point instructions, and the other two (U-pipe and V-pipe) execute integer instructions. This means that it is possible to execute three instructions simultaneously.

**Q.5** Write a short note on RS-232-C.

(8)

## Ans

The RS-232 standard is a collection of connection standards between different pieces of equipment. The EIA RS-232 serial communication standard is a universal standard, originally used to connect teletype terminals to modem devices. In a modern PC the RS-232 interface is referred to as a COM port. The COM port uses a 9-pin D-type connector (Refer Fig (a)) to attach to the RS-232 cable. The RS-232 standard defines a 25-pin D-type connector (Refer Fig (b)) but IBM reduced this connector to a 9-pin device so as to reduce cost and size.

Fig (a) Female & Male "DB-9" Connector

Fig 1(b) Female & Male "DB-25" Connector

**Q.6** Explain the terms: simplex, half duplex and full duplex.

(6)

## Ans

## **Simplex Transmission**

Data in a simplex channel is always one way. Simplex channels are not often used because it is not possible to send back error or control signals to the transmit end. An example of a simplex channel in a computer system is the interface between the keyboard and the computer, in that key codes need only be sent one way from the keyboard to the computer system.

## Half Duplex Transmission

A half duplex channel can send and receive, but not at the same time. It's like a onelane bridge where two-way traffic must give way in order to cross. Only one end transmits at a time, the other end receives.

## **Full Duplex Transmission**

Data can travel in both directions simultaneously. There is no need to switch from transmit to receive mode like in half duplex. It's like a two lane bridge on a two-lane highway.

Q.7 How DRAM's are different from SRAM's? Why DRAMs are said to employ address multiplexing? (4)

#### Ans

Dynamic RAM (DRAM) is essentially the same as SRAM, except that it retains data for only 2 or 4 ms on an internal capacitor. After 2 or 4 ms, the contents of the DRAM must be completely rewritten (refreshed) because the capacitors, which store logic 1 or logic 0, lose their charges. The entire content of the memory is refreshed with 256 reads in a 2-to-4 ms interval. Refreshing also occurs during a write, a read or during a special refresh cycle.

## **Q.8** Explain the operation of 8279. Explain the following terms:

- (i) N key Roll over.

- (ii) Key board debounce.

- (iii) FIFO RAM. (9)

## Ans

The 8279 is a programmable keyboard and display interfacing component that scans and encodes up to a 64-key keyboard and controls up to a 16-digit numerical display. The keyboard interface has built in first-in first-out (FIFO) buffer that allows it store up to eight keystrokes before the microprocessor must retrieve a character. The display section controls up to 16 numeric displays from an internal 16 X 8 RAM that stores the coded display information.

The keyboard section consists of eight lines that can be connected to eight columns of a keyboard, plus two additional lines as well as to shift and CNTL/STB keys. The key pressed are automatically debounced and the keyboard can operate in two modes two –key lock out or n-key rollover. If two keys in the two –key lock out mode are pressed simultaneously, only first key is recognized. In the N-key roll over mode, simultaneous key are recognized and their codes are stored in the internal buffer.

Q.9 What are the differences between CGA and VGA graphics adapters? (4)

## Ans

The Color Graphics Adapter (CGA), originally also called the Color/Graphics Adapter or IBM Color/Graphics Monitor Adapter introduced in 1981, was IBM's first color graphics card, and the first color computer display standard for the IBM PC.

The standard IBM CGA graphics card was equipped with 16 kilobytes of video memory, and could be connected either to a NTSC-compatible monitor or TV via an RCA jack, or to a dedicated 4-bit "RBGI" interface CRT monitor, such as the IBM 5153 color display.

The term Video Graphics Array (VGA) refers specifically to the display hardware first introduced with the IBM PS/2 line of computers in 1987, but through its widespread adoption has also come to mean either an analog computer display standard, the 15-pin D-subminiature VGA connector or the 640×480 resolution itself. While this resolution has been superseded in the personal computer market, it is becoming a popular resolution on mobile devices.

VGA was officially superseded by IBM's XGA standard, but in reality it was superseded by numerous slightly different extensions to VGA made by clone manufacturers that came to be known collectively as "Super VGA".

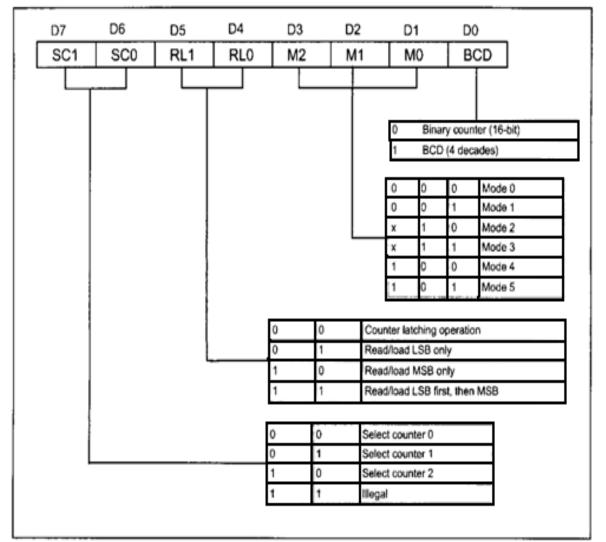

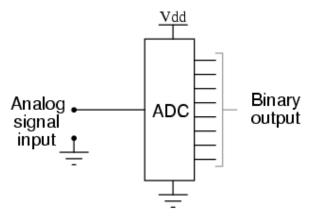

- Q.10 What do you mean by A/D conversion? Explain any one of the following A/D techniques:

- (i) Successive approximation.

- (ii) Parallel / flash converter.

## Ans

The electronic circuit, which translates an analog signal into a digital signal, is known as Analog - to – Digital converter (ADC).

(5)

## (i) Successive approximation ADC

One method of addressing the digital ramp ADC's shortcomings is the so-called successive approximation ADC. The only change in this design is a very special counter circuit known as a successive-approximation register. Instead of counting up in binary sequence, this register counts by trying all values of bits starting with the most significant bit and finishing at the least-significant bit. Throughout the count process, the register monitors the comparator's output to see if the binary count is less than or greater than the analog signal input, adjusting the bit values accordingly. The way the register counts is identical to the "trial-and-fit" method of decimal-to-binary conversion, whereby different values of bits are tried from MSB to LSB to get a binary number that equals the original decimal number. The advantage to this counting strategy is much faster results: the DAC output converges on the analog signal input in much larger steps than with the 0-to-full count sequence of a regular counter.

Without showing the inner workings of the successive-approximation register (SAR), the circuit looks like this:

Fig: Successive Approximation ADC Circuit

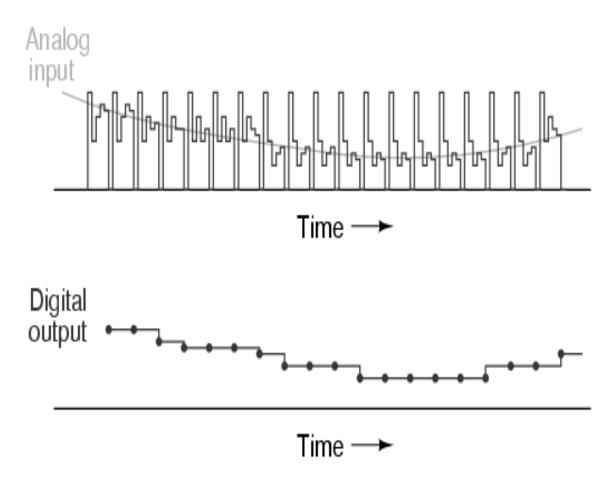

It should be noted that the SAR is generally capable of outputting the binary number in serial (one bit at a time) format, thus eliminating the need for a shift register. Plotted over time, the operation of a successive-approximation ADC looks like this:

Fig: Successive Approximation ADC Circuit Input and output Waveforms

#### ii. Parallel / flash converter.

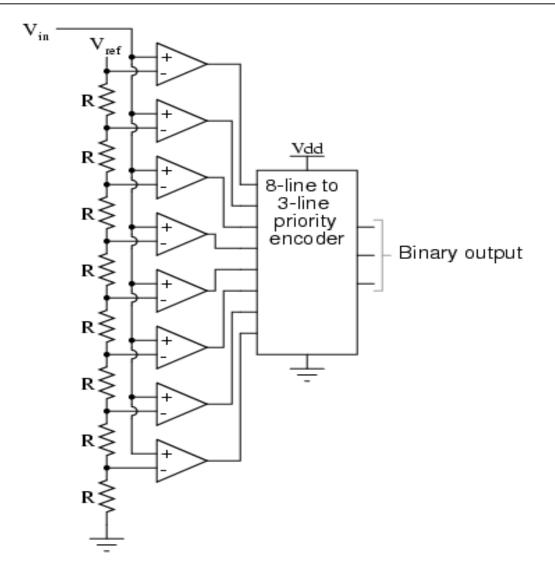

Also called the parallel A/D converter, this circuit is the simplest to understand. It is formed of a series of comparators, each one comparing the input signal to a unique reference voltage. The comparator outputs connect to the inputs of a priority encoder circuit, which then produces a binary output. The following illustration shows a 3-bit flash ADC circuit:

#### Fig: FLASH ADC Circuit

Vref is a stable reference voltage provided by a precision voltage regulator as part of the converter circuit, not shown in the schematic. As the analog input voltage exceeds the reference voltage at each comparator, the comparator outputs will sequentially saturate to a high state. The priority encoder generates a binary number based on the highest-order active input, ignoring all other active inputs.

Q.11 What do you mean by external and internal data bus? How are these two related in 8088 processor. (2)

Ans Internal Data Bus: A bus that operates only within the internal circuitry of the CPU, communicating among the internal caches of memory that are part of the CPU chip's design. This bus is typically rather quick and is independent of the rest of the computer's operations.

External Data Bus: A bus that connects a computer to peripheral devices. The 8088 microprocessor has 16-bit registers, 16-bit internal data bus and 20-bit address bus, which allows the processor address up to 1 MB of memory.

**Q.12** What is the difference between XT and AT computer system?

(2)

### Ans

XT ->extended and AT->Advanced Technology

Some differences between the PC and XT include the type of power supply originally included--63 vs 135 watts; the number and spacing of expansion slots--5 vs 8; the PC has a cassette tape interface connector on the back.

Q.13 What are program-invisible registers? (2)

Ans the global and local descriptor tables are found in the memory system. In order to access and specify the address of these tables, the program invisible registers used. The program invisible registers are not directly addressed by software so they are given name.

The GDTR (global descriptor table register) and IDTR (interrupt descriptor table register) contain the base addresses of the descriptor table and its limit. The limit of each descriptor table is 16 bits because the maximum table length is 64 Kbytes. When the protected mode operation is desired, the address of the global descriptor table and its limit are loaded into the GDTR.

Q.14 The interrupt vector table is always created in the first 1K area of the memory. Justify the statement. (2)

Ans When the CPU receives an interrupt type number from the PIC, it uses this number to look up the corresponding interrupt vector in memory. There are 256 interrupt types. Each interrupt vector occupies 4 bytes. Therefore, a total of 4 x 256 = 1K bytes of memory is reserved at the beginning of the processor memory address space for storing interrupt vectors.

Q.15 What is the purpose of carry (c) flag and zero (z) flag? (2)

**Ans** Carry flag holds the carry after addition or the borrow after subtraction. The carry flag also indicates error conditions, as dictated by some programs and procedures.

The Zero flag shows that the result of an arithmetic or logical operation is zero. If Z=1, the result is zero; if Z=0, the result is not zero.

Q.16 What is 16-bit ISA? Compare it with 8-bit ISA bus. (6)

**Ans** The only difference between the 8 and 16-bit ISA bus is that an additional connector is attached behind the 8-bit connector. 16-bit ISA card contains two edge connectors. One plugs into the original 8-bit connector and other plugs into the 16-bit connector. The added features that are most often used are the additional interrupt request inputs and DMA request signals. Interfaces found for the ISA bus are modems and sound cards.

Q.17 Compare memory mapped I/O with I/O mapped I/O. (4)

Ans Memory Mapped I/O Scheme: In this scheme there is only one address space. Address space is defined as all possible addresses that microprocessor

AC23

can generate. Some addresses are assigned to memories and some addresses to I/O devices. An I/O device is also treated as a memory location and one address is assigned to it. In this scheme all the data transfer instructions of the microprocessor can be used for both memory as well as I/O device. This scheme is suitable for a small system.

In I/O mapped I/O scheme the addresses assigned to memory locations can also be assigned to I/O devices. Since the same address may be assigned to a memory location or an I/O device, the microprocessor must issue a signal to distinguish whether the address on the address bus is for a memory location or an I/O device.

Q.18 Explain in brief the functions of the clock generator chip, 8284. (4)

# Ans, 8284 Clock generator:

The 8284 is an ancillary component to the microprocessors. Without clock generator, many additional circuits are required to generate the clock in an microprocessor based system. A 8284 provides the following basic functions or signals: Clock generation, RESET synchronization, READY synchronization, and a TTL-level peripheral clock signal.

Q.19 Write a brief note on MMX technology. (4)

**Ans**, MMX (Multimedia extensions) technology adds 57 new instructions to the instruction set of the Pentium – 4 microprocessors. The MMX technology also introduces new general purpose instructions. The new MMX instructions are designed for application such as motion video, combined graphics with video, image processing, audio synthesis, speech synthesis and compression, telephony, video conferencing, 2D graphics, and 3D graphics. These new instructions operate in parallel with other operations as the instruction for the arithmetic coprocessor.

The MMX architecture introduces new packed data types. The data types are eight packed, consecutive 8-bit bytes; four packed, consecutive 16-bit words; and two packed, consecutive 32-bit double words.

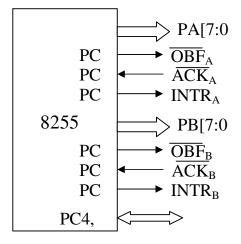

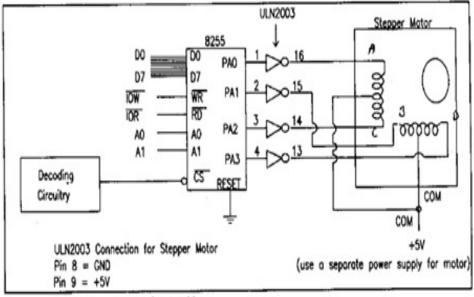

Q.20 What are the different modes in which 8255 Programmable Peripheral Interface (PPI) can operate? Write the 8086 initialisation routine required to program 8255 for mode 1 with Port A and Port B as output Ports and Port C as an input port. Indicate all the relevant signals.

## Ans

- 24 I/O lines in 3 8-bit port groups A, B, C

- A, B can be 8-bit input or output ports

- C can serve as 2 4-bit input or output ports

- 3 modes of operation:

- Mode 0:A, B, C simple input or output level sensitive ports

- Mode 1:A, B input or output ports with strobe control in C

- Mode 2:A is bidirectional with control/handshake in B and C

- A, B can only change 1 byte at a time

- C has individual bit set/reset capability

- Advantage is non-dedicated circuit can change port configuration with software and no "glue logic"

- Ports A, B, and C are used for I/O data.

- The control register is programmed to select the operation mode of the three ports A, B, and C.

- Mode 0 : simple I/O mode

- Any of the ports A, B, CL and CU can be programmed as input or output.

- No control of individual bits (all bits are out or all bits are in)

#### Mode0:

Mode 0 operation causes the 82C55 to function as a buffered input device or as a latched output device.

In previous example, both ports A and B are programmed as (mode 0) simple latched output ports.

Port A provides the segment data inputs to display and port B provides a means of selecting one display position at a time.

The values for the resistors and the type of transistors used are determined using the current requirements (see text for details).

Textbook has the assembly code fragment demonstrating its use.

Examples of connecting LCD displays and stepper motors are also given.

#### Mode1:

Port A and/or port B function as latching input devices. External data is stored in the ports until the microprocessor is ready.

Port C used for control or handshaking signals (cannot be used for data).

Signal definitions for Mode 1 Strobed Input

- **STB** The strobe input loads data into the port latch on a 0-to-1 transition

- **IFB Input buffer full** is an output indicating that the input latch contain information

- **INTR** Interrupt request is an output that requests an interrupt

- **INTE** The **interrupt enable signal** is neither an input nor an output; it is an internal bit programmed via the PC4(port A) or PC2(port B) bits.

- **PC7,PC6** The port C pins 7 and 6 are general-purpose I/O pins that are available for any purpose.

(8)

# AC23

## Mode2:

Only allowed with port A. Bi-directional bused data used for interfacing two computers, GPIB interface etc.

| INTR        | Interrupt request is an output that requests an interrupt                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------|

| OBF         | <b>Output buffer full</b> is an output indicating that the output buffe: contains data for the bi-directional bus              |

| ACK         | Acknowledge is an input that enables tri-state buffers which are otherwise in their high-impedance state                       |

| STB         | The strobe input loads data into the port A latch                                                                              |

|             | <b>T 1 1 1 1 1 1 1 1 1 1</b>                                                                                                   |

| IFB         | <b>Input buffer full</b> is an output indicating that the input latch contains information for the external bi-directional bus |

| IFB<br>INTE |                                                                                                                                |

Q.21 Explain the operation of IRET instruction. What memory locations contain the vector for an INT 34 instruction? (4)

## Ans

The Interrupt return (IRET) instruction is used only with software or hardware interrupt service procedures. Whenever an IRET instruction executes, it stores the contents of I and T from the stack. This is important because it preserves the state of the flag bits. If interrupts were enabled before an interrupt service procedure, they automatically re-enabled by the IRET instruction because it restores the flag register.

Interrupt Number 20-FF are stored at an address 80 – 3FFH.

- Q.22 Explain the following terms:

- i. Branch prediction logic.

- ii. Paging.

- iii. Assembler.

- iv. Microprocessor development system.

## Ans

(i) Branch prediction logic in Pentium: The Pentium microprocessor uses branch prediction logic to reduce the time required for a branch caused by internal delays. These delays are minimized because when a branch instruction is encountered, the microprocessor begins pre-fetch instruction at the branch address. The instructions are loaded into the instruction cache, so when the branch occurs, the instructions are present and allow the branch to execute in one clocking period. If for any reason the branch prediction logic errors, the branch requires an extra three clocking periods to execute. In most cases, the branch prediction is correct and no delay ensues. (ii) Paging Unit: The paging mechanism functions with 4K – byte memory pages or with a new extension available to the Pentium with 4M byte-memory pages. In the Pentium, with the new 4M-byte paging feature memory for the page-table reduced to single page table.

(iii) Assembler: An assembler or macro-assembler generally forms a part of the operating system. Which translates a assembly language program into machine language program.

(iv) Microprocessor development system: Computer systems have undergone many changes recently. Machines that once filled large areas have been reduced to small desktop computer systems because of the microprocessor. Although these desktop computers are compact, they possess computing power that was only dreamed of a few years ago.

The blocks of the microprocessor based system are

- 1. The Memory and I/O System

- 2. The DOS Operating System

- 3. The Microprocessor

Q.23 Explain the following instructions: (i) TEST (ii) NEG (iii) CMP (iv) DAA. (8)

#### Ans

(i) TEST: The TEST instruction performs the AND operation. The difference is that the AND instruction changes the destination operand, while the TEST instruction does not. A TEST only affects the condition of the flag register, which indicates the result of the test.

(ii) NEG: Arithmetic sign inversion or two's complement (NEG). The NEG instruction two's complements a number, which means that the arithmetic sign of a signed number changes from positive to negative or from negative to positive.

(iii)CMP: The comparison instruction (CMP) is a subtraction that changes only the flag bits; the destination operand never changes. A comparison is useful for checking the entire contents of a register or a memory location against another value. A CMP is normally followed by a conditional jump instruction, which tests the condition of the flag bits

(iv)DAA: The DAA instruction follows the ADD or ADC instruction to adjust the result into a BCD result. The DAA instruction functions only with the AL register, this addition must occur eight bits at a time.

- **Q.24** With respect to serial communication define the following:

- (i) baud rate.

(ii) asynchronous communication.

- (iii) parity.

- (iv) half duplex. (4)

#### Ans

Half Duplex Transmission: A half duplex channel can send and receive, but not at the same time. It's like a one-lane bridge where two-way traffic must give way in order to cross. Only one end transmits at a time, the other end receives. Asynchronous means "no synchronization", and thus does not require sending and receiving idle characters. However, the beginning and end of each byte of data must be identified by start and stop bits. The start bit indicates when the data byte is about to begin and the stop bit signals when it ends. The requirement to send these additional two bits causes asynchronous communication to be slightly slower than synchronous however it has the advantage that the processor does not have to deal with the additional idle characters.

The rate of data transfer in serial data communication is denoted in bps. Bits per second (bps) is the rate of transfer of information bits. Baud is the number of signal level changes per second in a line, regardless of the information content of those signals. The baud and bps rates are not necessarily equal. The ratio of BPS to baud depends on the information-coding scheme that you are using. For example, each character in asynchronous RS-232 coding includes a start and stop bit that are not counted as information bits, so the BPS rate is actually less than the baud rate.

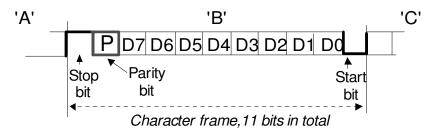

Besides the synchronization provided by the use of start and stop bits, an additional bit called a parity bit may optionally be transmitted along with the data. Figure shows the inclusion of an additional parity bit for error control purposes. A parity bit affords a small amount of error checking, to help detect data corruption that might occur during transmission. You can choose even parity, odd parity, mark parity, space parity or none at all. When even or odd parity is being used, the numbers of marks (logical 1 bit) in each data byte are counted, and a single bit is transmitted following the data bits to indicate whether the number of 1 bit just sent is even or odd.

Fig. Framed data including a parity bit

For example, when even parity is chosen, the parity bit is transmitted with a value of 0 if the number of preceding marks is an even number. For the binary value of 0110 0011 the parity bit would be 0. If even parity were in effect and the binary number 1101 0110 were sent, then the parity bit would be 1.

Q.25 What is the importance of RS232-C in serial communication? Name some application where you see its use. (4)

**Ans** RS-232 stands for Recommend Standard number 232 and C is the latest revision of the standard. The serial ports on most computers use a subset of the RS-232C standard. The full RS-232C standard specifies a 25-pin "D" connector of which 22 pins are used. Most of these pins are not needed for normal PC communications, and indeed, most new PCs are equipped with male D type connectors having only 9 pins. In the world of serial communications, there are two different kinds of equipment:

- DTE Data Terminal Equipment

- DCE Data Communications Equipment

#### Q.26 Write short notes on (Any FOUR):-

- (i) 8259.

- (ii) Real time clock.

- (iii) Real and protected mode.

- (iv) Super scalar architecture.

- (v) Comparison between Motorola processors and INTEL processors.

#### $(4 \times 4 = 16)$

#### Ans

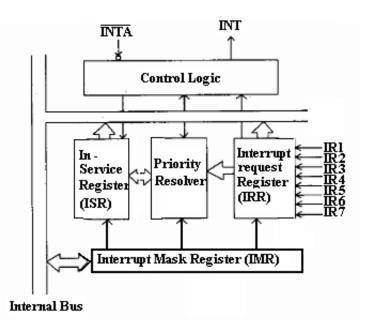

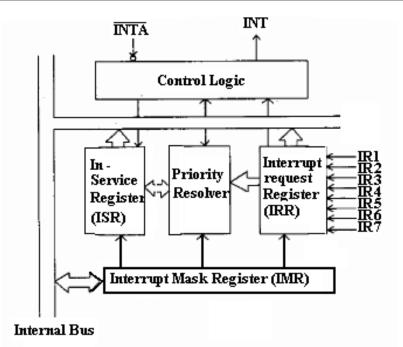

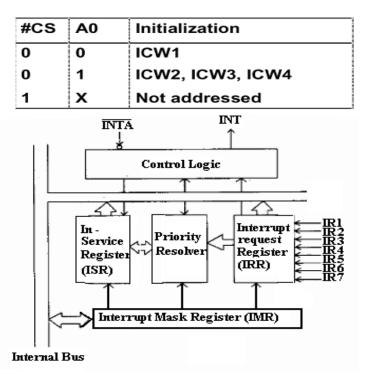

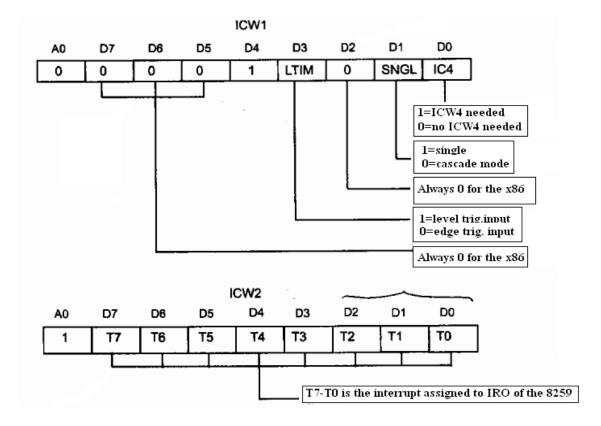

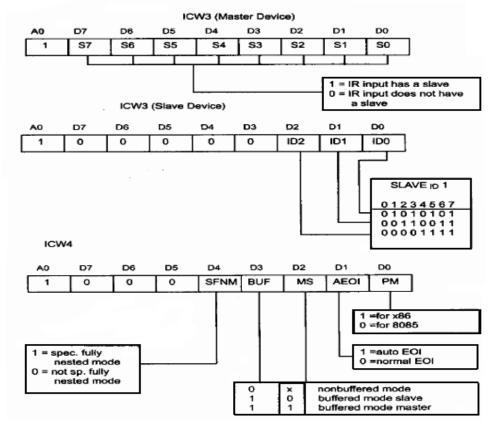

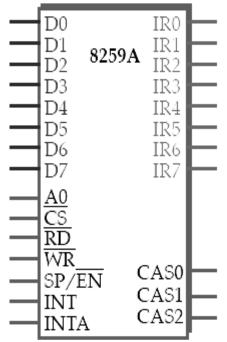

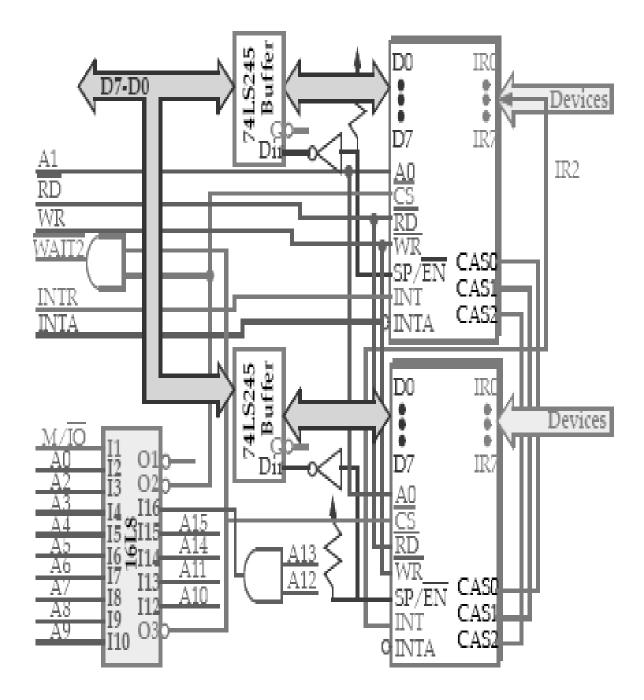

#### (i) 8259:

The 8259A adds 8 vectored priority encoded interrupts to the microprocessor. It can be expanded to 64 interrupt requests by using one master 8259A and 8 slave units. CS and WR must be decoded. Other connections are direct to microprocessor.

The pins D7 – D0: the bidirectional data connection, IR7 – IR0: Interrupt request, used to request an interrupt & connect to a slave in a system with multiple 8259A. WR :-Connects to a write strobe signal (lower or upper in a 16 bit system), RD :-Connects to the IORC signal , INT :- Connects to the INTR pin on the microprocessor from the master and is connected to a IR pin on a slave and INTA :- Connects to the INTA pin on the microprocessor. In a system only the master INTA signal is connected

A0 :- Selects different command words with in the 8259A, CS :- Chip select - enables the 8259A for programming and control, SP/EN :- Slave Program (1 for master, 0 for slave)/Enable Buffer (controls the data bus transceivers in a large microprocessor based system when in buffered mode) and CAS2-CAS0 :- Used as outputs from the master to the slaves in cascaded systems.

Internal Bus

#### (ii) Real time clock:

A real-time clock keeps the time in real time – that is, in hours and minutes. The software for the real-time clock contains an interrupt service procedure that is called 60 times per second and a procedure that updates the count located in four memory locations.

#### Assembler directives:

An assembler directive is a statement to give direction to the assembler to perform the task of assembly process. The assembler directives control organization of the program and provide necessary information to the assembler to understand assembly language programs to generate machine codes. They indicate how an operand or section of a program is to be processed by the assembler. An assembler supports directives to define data, to organize segments to control procedures, to define macros etc.

#### (iii) Real and protected mode:

**Operation of Real mode interrupt:** When the microprocessor completes executing the current instruction, it determines whether an interrupt is active by checking (1) instruction execution, (2) single –step, (3) NMI, (4) co-processor segment overrun, (5) INTR, and (6) INT instruction in the order presented. If one or more of these interrupt conditions are present, the following sequence of events occurs:

- 1. The contents of the flag register are pushed onto the stack

- 2. Both the interrupt (IF) and trap (TF) flags are cleared. This disables the INTR pin and the trap or single-step feature.

- 3. The contents of the code segment register (CS) are pushed onto the stack.

- 4. The contents of the instruction pointer (IP) are pushed onto the stack.

- 5. The interrupt vector contents are fetched, and then placed into both IP and CS so that the next instruction executes at the interrupt service procedure addressed by the vector.

#### **Protected mode interrupt:**

In the protected mode, interrupts have exactly the same assignments as in real mode, but the interrupt vector table is different. In place of interrupt vectors, protected mode uses a set of 256 interrupt descriptors that are stored in an interrupt descriptor table (IDT).

#### (iv). Super scalar architecture:

The Pentium microprocessor is organized with three execution units. One executes floating-point instructions, and the other two (U-pipe and V-pipe) execute integer instructions. This means that it is possible to execute three instructions simultaneously.

#### (v). Comparison between Motorola processors and INTEL processors:

AMD/Intel processors are really about the same thing. They run the same software and operate in a very similar manner. AMD is often less expensive than Intel, and depending on what you use a computer for one may be somewhat faster than the other.

Motorola has been largely relegated to the "also-ran" category of microprocessor manufactures since Apple computer stopped using them in favor of the IBM Power PC processor (Apple has since switched to Intel).

Motorola had an excellent 32 bit processor design years before Intel. Furthermore, the design of the Motorola 68000 processor line (from a programmer's perspective) was immensely better. The two major features of the 68000 line that made this true were

1) Orthogonality of register access and

2) Number of registers available.

These features made writing code for Motorola CPUs much simpler.

Q.27 What is (i) USB (ii) AGP (iii) XMS (iv) EMS (v) TSR (vi) EDO RAM (6)

Ans

(i). **USB:** The USB (UNIVERSAL SERIAL BUS) is intended to connect peripheral devices such as keyboards, a mouse, modems, and sound cards to the microprocessor through a serial data path and a twisted pair of wires. The main idea is to reduce system cost by reducing the number of wires. Another advantage is that the sound system can have a separate power supply from the PC, which means less noise. The data transfer rates through the USB are 12 Mbps at present.

(ii). **AGP:** The latest addition to many computer systems is the inclusion of the **accelerated graphics port** (AGP). The AGP operates at the bus clock frequency of the microprocessor. It is designed so that a transfer between the video card and the system memory can progress at a maximum speed. The AGP can transfer data at a maximum rate of 528M bytes per second. This port probably will never be used for any devices other than the video card.

(iii). **XMS**: The memory system is divided into three main parts. TPA (transient program area), system area, and XMS (extended memory system). The type of microprocessor in your computer determines whether an extended memory system exists.

(iv). **EMS:**The area at location C8000H-DFFFFFH is often open or free. This area is used for the **expanded memory system** in a PC or XT system, or for the upper memory system in an AT system. The EMS allows a 64K-byte page frame of memory to be used by application programs.

(v). **TSR:**The TPA also holds TSR (terminate and stay resident) programs that remain in memory in an active state until activated by a hot-key sequence or another event such as an interrupt.

(vi). **EDO RAM:**A slight modification to the structure of the DRAM changes the device into an EDO (extended data output) DRAM device. In the EDO memory, any memory access, including a refresh, stores the 256 bits selected by RAS' into latches. These latches hold the next 256 bits of information, so in most programs, which are sequentially executed, that data are available without any wait states.

Q.28 What are program invisible registers? Explain the purpose of the GDTR. If the microprocessor sends linear address 00200000H to the paging mechanism, which paging directory entry and which page table entry is accessed? (3)

**Ans**, the global and local descriptor tables are found in the memory system. In order to access and specify the address of these tables, the program invisible registers used. The program invisible registers are not directly addressed by software so they are given name.

The GDTR (global descriptor table register) and IDTR (interrupt descriptor table register) contain the base addresses of the descriptor table and its limit. The limit of each descriptor table is 16 bits because the maximum table length is 64 Kbytes. When the protected mode operation is desired, the address of the global descriptor table and its limit are loaded into the GDTR.

For linear address 0000000H - 003FFFFFH, the first entry of the page directory is accessed. Each page directory entry represents or repages a 4-Mbyte section of the memory system. The contents of the page directory select a page table that is indexed by the next 10 bits of the linear address. This means that address 0000000H - 00000FFFH selects page directory entry 0 and page table entry 0.

Q.29 Discuss the salient features of a parallel programmable interface, 8255. (4)

#### Ans

- 24 I/O lines in 3 8-bit port groups A, B, C

- A, B can be 8-bit input or output ports

- C can serve as 2 4-bit input or output ports

- 3 modes of operation:

- Mode 0:A, B, C simple input or output level sensitive ports

- Mode 1:A, B input or output ports with strobe control in C

- Mode 2:A is bidirectional with control/handshake in B and C

- A, B can only change 1 byte at a time

- C has individual bit set/reset capability

- Advantage is non-dedicated circuit can change port configuration with software and no "glue logic"

- Ports A, B, and C are used for I/O data.

- The control register is programmed to select the operation mode of the three ports A, B, and C.

- Mode 0 : simple I/O mode

- Any of the ports A, B, CL and CU can be programmed as input or output.

- No control of individual bits (all bits are out or all bits are in)

- Mode 1: Ports A and B can be used as input or output ports with handshaking.

- Mode 2 : Port A can be used as bidirectional I/O port with handshaking

- Q.30 What do you understand by assembler directives? What do the following assembler directives do?

- (i) ASSUME

- (ii) SEGMENT

- (iii) DB

- (iv) PUBLIC

#### Ans

(i) **ASSUME:** This directive will be used to map the segment register names with memory addresses.

The Syntax is as follows:

(8)

ASSUME SS: Stackseg, DS : Dataseg, CS:Codeseg

The ASSUME will tell the assembler to use the SS register with the address of the stack segment whose name is stackseg.

(ii) **SEGMENT:** This directive defines to the assembler the start of a segment with name segment-name. The segment name should be unique and follows the rules of the assembler

The Syntax is as follows:

Segment Name SEGMENT {Operand (Optional)}; Comment

Segment Name ENDS.

(iii) **DB** (**Define Byte**): The DB directive defines a byte-type variable (i.e. a variable which occupies one byte of memory space). In a given directive statement, there may be single initial value or multiple values of the defined variable. If there is one initial value, one byte of memory space is reserved. If there are multiple values, one byte of memory space is reserved for each value. The general format is:

Name of Variable DB Initial value or values.

(iv) The **PUBLIC** and EXTRN directives are very important to modular programming. PUBLIC used to declare that labels of code, data, or entire segments are available to other program modules. EXTRN (external) declares that labels are external to modules. Without these statements, modules could not be linked together to create a program by using modular programming techniques. They might link, but one module would not be able to communicate to another.

The PUBLIC directive is placed in the opcode field of an assembly language statement to define a label as public, so that the label can be used by other modules.

Q.31 Discuss the role of a bus arbiter in a multiprocessor configuration. (4)

**Ans**, Bus arbiter: Which functions to resolve priority between bus masters and allows only one device at a time to access the shared bus. The 8289 bus arbiter controls the interface of a bus master to a shared bus. This is designed to function with the 8086/8088 microprocessors. Each bus master or microprocessor requires an arbiter for the interface to the shared bus, which Intel calls the MULTIBUS and IBM calls the MICRO CHANNEL.

The shared bus used only to pass information from one microprocessor to another; otherwise, the bus master function in their own local bus modes by using their own local programs, memory, and I/O space. Microprocessors connected in this kind of system are often called parallel or distributed processors because they can execute software and perform tasks in parallel.

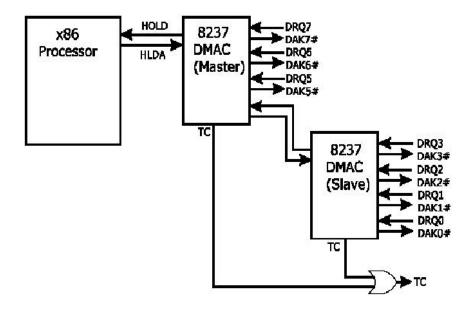

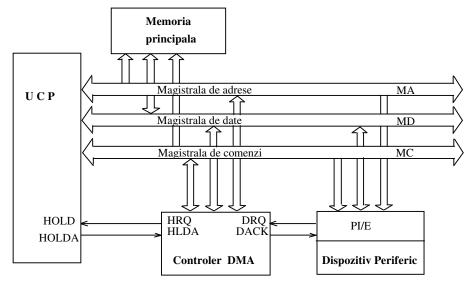

Q.32 Show how a typical DMA controller can be interfaced to an 8086/8085 based maximum mode system.

(8)

Ans, For 8088 in maximum mode:

The RQ/GT1 and RQ/GT0 pins are used to issue DMA request and receive acknowledge signals. Sequence of events of a typical DMA process

1) Peripheral asserts one of the request pins, e.g. RQ/GT1 or RQ/GT0 (RQ/GT0 has higher priority)

2) 8088 completes its current bus cycle and enters into a HOLD state

3) 8088 grants the right of bus control by asserting a grant signal via the same pin as the request signal.

4) DMA operation starts

5) Upon completion of the DMA operation, the peripheral asserts the request/grant pin again to relinquish bus control.

# Q.33 What is a co-processor? What is its use in a typical microprocessor based system. (8)

**Ans** 8087 NDP (numerical data processor) is also known as math co-processor which is used in parallel with the main processor for number crunching applications, which would otherwise require complex programming. It is also faster than 8086/8088 processor in performing mathematical computation. It has its own specialized instruction sets to handle mathematical programs.

It is a processor which works in parallel with the main processor. It has its own set of specialized instructions. The number crunching part of the program is executed by 8087. Instruction for 8087 are written in the main program interspersed with the 8086 instructions. All the 8087 instruction codes have 11011 as the most significant bits of their first code byte.

Q.34 What is segmentation? What are its advantages? How is segmentation implemented in typical microprocessors? (8)

## Ans

Segment memory addressing divides the memory into many segments. Each of these segments can be considered as a linear memory space. Each of these segment is addressed by a segment register.

However since the segment register is 16 bit wide and the memory needs 20 bits for an address the 8086 appends four bits segment register to obtain the segment address. Therefore, to address the segment 10000H by , say the SS register, the SS must contain 1000H.

The first advantage that memory segmentation has is that only 16 bit registers are required both to store segment base address as well as offset address. This makes the internal circuitry easier to built as it removes the requirement for 20 bits register in case the linear addressing method is used. The second advantage is relocatability.

Q.35 What is a PCI bus? Discuss its features and usage.

#### Ans

Peripheral Component Interconnect (PCI): This bus was developed by Intel and introduced in 1993. It is geared specifically to fifth- and sixth-generation systems, although the latest generation 486 motherboards use PCI as well.

PCI bus has plug – and – play characteristics and the ability to function with a 64-bit data bus. A PCI interface contains series of registers, located in a small memory device on the PCI interface that contains information about the board.

**Q.36** How is EISA bus different from ISA bus?

(4)

(6)

## Ans

The Extended Industry Standard Architecture (EISA) is a 32 bit modification to the ISA bus. As computers became larger and had wider data buses, a new bus was needed that would transfer 32-bit data. The clocking speed limited up to 8MHz. The most common application for the EISA bus is a disk controller or as a video graphics adapter. These applications benefit from the wider data bus width because the data transfer rate for these devices are high.

Q.37 Differentiate between synchronous and asynchronous types of serial communication.

(6) Ans Serial data communication uses two basic types, synchronous and asynchronous. With synchronous communications, the two devices initially synchronize themselves to each other, and then continually send characters to stay in sync. Even when data is not really being sent, a constant flow of bits allows each device to know where the other is at any given time. That is, each character that is sent is either actual data or an idle character.

Asynchronous means "no synchronization", and thus does not require sending and receiving idle characters. However, the beginning and end of each byte of data must be identified by start and stop bits. The start bit indicates when the data byte is about to begin and the stop bit signals when it ends. The requirement to send these additional two bits causes asynchronous communication to be slightly slower than synchronous however it has the advantage that the processor does not have to deal with the additional idle characters.

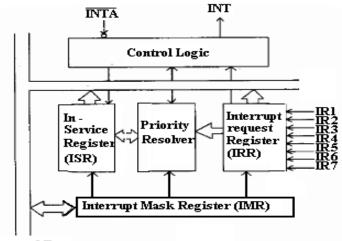

**Q.38** Draw and explain the block diagram of programmable interrupt controller 8259.

(8)

**Ans** The 8259A adds 8 vectored priority encoded interrupts to the microprocessor. It can be expanded to 64 interrupt requests by using one master 8259A and 8 slave units. CS and WR must be decoded. Other connections are direct to microprocessor.

The pins D7 – D0: the bidirectional data connection, IR7 – IR0: Interrupt request, used to request an interrupt & connect to a slave in a system with multiple 8259A. WR :-Connects to a write strobe signal (lower or upper in a 16 bit system), RD :-Connects to the IORC signal , INT :- Connects to the INTR pin on the microprocessor from the master and is connected to a IR pin on a slave and INTA :- Connects to the INTA pin on the microprocessor. In a system only the master INTA signal is connected

A0 :- Selects different command words with in the 8259A, CS :- Chip select - enables the 8259A for programming and control, SP/EN :- Slave Program (1 for master, 0 for slave)/Enable Buffer (controls the data bus transceivers in a large microprocessor based system when in buffered mode) and CAS2-CAS0 :- Used as outputs from the master to the slaves in cascaded systems.

Fig: 8259 Block Diagram

Q.39 Discuss the various types of memory devices that you are familiar with. (8)

#### Ans

All of the memory used as main store in a modern computer is implemented as semiconductors fabricated on wafers of silicon. Semiconductor memory is fast and easy to use. To fulfil the needs of modern computer systems it is becoming increasingly dense (more bits per chip) and cheap.

A semiconductor memory chip consists of a large number of cells organized into an array, and the logic necessary to access any array in the cell easily. Semiconductor memory may be classed according to the mechanism used by each cell to store data. The simplest type of memory is called static memory. In static memory each cell uses a flip-flop made from four or six transistors. The data in each cell is remembered until the power is switched off. Static memory is easy to use and reliable, but is relatively bulky, slow and expensive. Most computer systems therefore use dynamic memory as their main store. Dynamic memory uses just a single transistor per cell, and is therefore denser, faster and cheaper. Unfortunately each cell gradually forgets the data stored in it, and so extra circuitry must be used to continually refresh the cells.

Memory, with regard to computers, most commonly refers to semiconductor devices whose contents can be accessed (i.e., read and written to) at extremely high speeds. The main characteristics of semiconductor memory are based on capacity, organization and access time. In microprocessor-based systems semiconductor memories are used as primary storage for code and data.

In contrasts with storage, which (1) retains programs and data regardless of whether they are currently in use or not, (2) retains programs and data after the power supply has been disconnected, (3) has much slower access speeds and (4) has a much larger capacity (and a much lower cost). Examples of storage devices are hard disk drives (HDD), floppy disks, optical disks (e.g., CDROMS and DVDs) and magnetic tape.

The term memory as used in a computer context originally referred to the magnetic core memory devices that were used beginning in the 1950s. It was subsequently applied to the semiconductor memory devices that replaced core memories in the 1970s.

Computer memory today consists mainly of dynamic random access memory (DRAM) chips that have been built into multi-chip modules that are, in turn, plugged into slots on the motherboard (the main circuit board on personal computers and workstations). This DRAM is commonly referred to as RAM (random access memory), and it constitutes the main memory of a computer.

The random in random access memory refers to the fact that any location in such memory can be addressed directly at any time. This contrasts with sequential access media, such as magnetic tape, which must be read partially in sequence regardless of the desired content.

There are three basic kinds of memory used in microprocessor systems - commonly called ROM, RAM, and hybrid. ROM and RAM are - "Read Only Memory" and "Random Access Memory". The program may be stored in ROM or RAM - the program does not normally change while it executes - while data is stored in the registers and RAM. Of course, if you turn off the chip and turn it on again, you have lost all the contents of the registers, and RAM.

In a typical computer, as much as possible is in RAM, to give the maximum possible flexibility; you have basic programmes allowing you to interact with discs, keyboards and the display in ROM, and load in as much of the software as possible when you run the programs.

Q.40 Write explanatory notes on Microprocessor development system. (16)

Ans,

## Microprocessor development system:

Computer systems have undergone many changes recently. Machines that once filled large areas have been reduced to small desktop computer systems because of the microprocessor. Although these desktop computers are compact, they possess computing power that was only dreamed of a few years ago.

The blocks of the microprocessor based system are

- 1. The Memory and I/O System

- 2. The DOS Operating System

- 3. The Microprocessor

- Q.41 Discuss DOS function call and BIOS function call with one example of each. (5)

## Ans

## **DOS function call:**

In order to use DOS function calls, always place the function number into register AH and load all other pertinent information into registers, as described in the entry data table (Refer Text1-page no 809). Once this is accomplished, follow with an INT 21H to execute the DOS function.

Example: MOV AH, 6

MOV DL, 'A'

INT 21H.

Example shows how to display an ASCII A on the CRT screen at the current cursor position with a DOS function call.

BIO stands for Basic Input Output System. It is a set of programs to provide most basic low-level services such as services keyboard, disks, serial port, printer, display, and bootstrap. BIOS programs are stored in a ROM. When power is switched on ROM-BIOS takes the control of a computer. First of all, ROM-BIOS programs for power-on-self test are executed. These tests check that whether the computer is in proper working order after this test, the process of loading the operating system into main memory is called booting. ROM-BIOS contains a program called bootstrap loader, this directs CPU to read from the disk a specific program called boot and to load it into main memory.

**BIOS function calls** are found stored in the system and video BIOS ROMs. These BIOS ROM function directly control the I/O devices, with or without DOS loaded into a system.